近年ナノフォトニクスデバイスを用いた光論理回路は,超高速な動作が見込めるために注目を集めている.

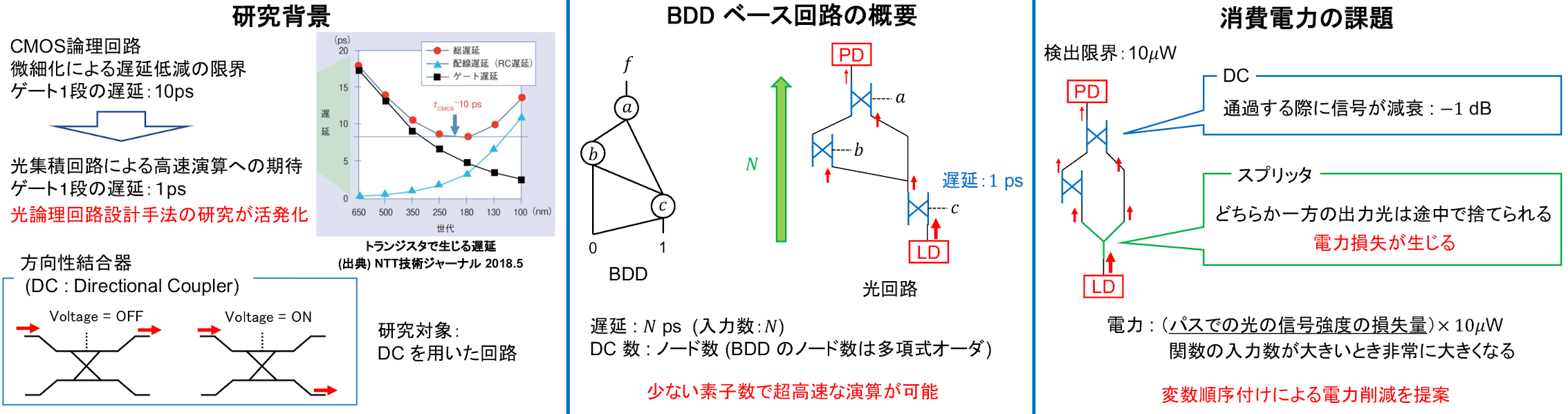

BDD ( 二分決定グラフ ) に基づく光論理回路は光の高速性を活かすことができる ため に BDD に基づく論理合成手法が主に研究されている.しかし, BDD に基づく回路は消費電力が非常に大きくなる課題を持つ.この課題への対策として,本研究では BDD の変数順序付けによる電力削減を検討する. BDD の変数順序付けの先行研究について紹介し,それらの手法を光論理回路の消費電力削減に適用する際の課題を述べる.さらにそれらの課題を考慮した変数順序最適化アルゴリズムを提案する.

情報社会の発展とともに低遅延処理が必要なアプリケーションが増えている.しかし,CMOS 論理ゲートの微細化による悪影響の顕在化により CPU の周波数応答性の進展性は頭打ち状態である.そこで光論理回路により低遅延性の進展の限界を克服することが期待されている.ナノフォトニクスデバイスが発展し,演算処理を光論理回路で実装することが実用的になり,光論理回路向けの CAD ツールの需要が高まる時代に本研究は重要な基礎的技術になる.

| 氏名 | 専攻 | 研究室 | 役職/学年 |

|---|---|---|---|

| 松尾 亮祐 | 通信情報システム専攻 | 湊研究室 | 博士1回生 |

| 湊 真一 | 通信情報システム専攻 | 湊研究室 | 教授 |